728x90

※ HDL 프로그래밍 -> 하드웨어 디자인을 하는 것이지 소프트웨어 프로그래밍과 다르다는 것을 알아둬야함

-> 이를 위해서 특성을 잘 알고 회로를 설계 잘하는 것을 아는 것이 중요함 ※

Velilog HDL 구문

1. 논리 합성 - ex. assign, if~else, case, for, always

2. Simulation - ex. initial, $finish, $fopen

(논리 합성이 지원되지 않음)

3. Liberay - ex. specify, $width, table

(이번 강좌에서는 공부하지 않음)

Velilog HDL 구문 개요

module: 기본 설계 단위

module module_name (port_list(목록));

//

port 선언

reg 선언

wire 선언

parameter 선언//

// 하위 모듈 호출 _ 회로의 기능 동작 구조

always, initial문

function, task 정의문

assign 문

function, task 호출문//

end module()

(file에 module 하나 저장해서 관리함)

반가산기 회로 모델링 예제

코드

# 게이트 프리미티브를 이용한 모델링

# 게이트 프리미티브를 이용한 모델링

module half_adder(a,b,cout);

input a, b; # 입력 신호 정의, 1-bit

output sum, cout; # 출력 신호 정의, 1-bit

wire cout_bar;

# 자료형: 1. net(wire), 2. variable

xor(sum,a,b); # 출력부터 기입

nand(cout_bar,a,b);

not(cout, count_bat);

endmodule

# 연속 할당문을 이용한 모델링(동시에 할당)

# 연속 할당문을 이용한 모델링(동시에 할당)

module half_adder2(a,b,sum,cout);

# 포트 선언

intput a,b;

output sum, cout;

assign cout = a & b; # '=' -> 할당, '&' -> AND 연산자

assign sum = a ^ b; # '^' -> XOR 연산자

# 순서가 바뀌어도 같은 결과가 나옴_(하드웨어적 특성, 절차형이 아님)

endmodule

조합 논리회로 모델링

# 행위 수준 모델링

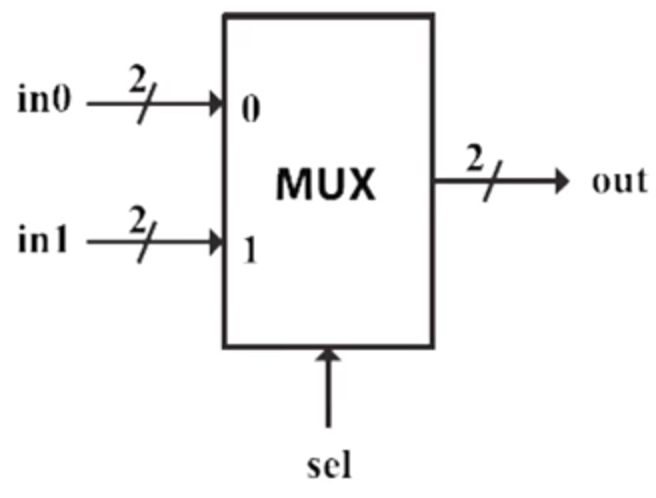

- input: 2 bit in0, in1

- 구조: 2:1 MUX(multiplexer)

sel= 0 -> output= in0

sel= 1 -> output= in1

# 행위 수준 모델링

module mux2b_if (in0, in1, sel, out);

input [1:0] in0, in1; # [1:0] -> 벡터(다중 비트_2-bit)

input sel; #1-bit

output [1:0] out; #2-bit

reg [1:0] out; #2-bit variable 자료형(절차형 할당문 안에 들어가는 자료형)

# always 안의 구문은 절차형 할당문(순서가 영향을 미침)

always @ (sel or in0 or in1) begin # '@' -> event operator(괄호안에 신호들의 변화를 감지)

if (sel ==0) # '==' -> 등가 연산자

out = in0;

else

out = in1;

end

endmodule

순차회로 모델링

# 행위 수준 모델링

- 구조: 클록의 상승 엣지에서 동작하는 D-플립플롭

# 행위수준 모델링

module D_ff (clk, din, rst, q);

input clk, din, rst;

output q;

reg q;

always @(posedge clk or posedge rst) # 'posedge' -> 상승 천이, posedge clk -> 상승 엣지가 발견될 때

begin

if (rst == 1)

q <= 0; # q를 0으로 초기화 (비동기식)

else

q <= din; # q를 din으로 할당해라

end

endmodule

# 하위 모듈 인스턴스를 이용한 구조적 모델링

# 하위 모듈 인스턴스를 이용한 구조적 모델링(전가산기)

module full_add(a, b, cin, sum, cout);

input a, b, cin;

output sum, cout;

wire w1, w2, w3; //1비트 wire 선언은 생략 가능

half adder U1 (.a(a), .b(b), .sum(w1), .cout(w2)); // 이름에 의한 포트 매핑 '.sum(w1)' -> sum이라는 포트에는 w1신호

half adder U2 (w1, cin, sum, w3); // 순서에 의한 포트 매핑(순서대로 포트 매핑)

or U3 (cout, w2, w3); // 게이트 프이미티브 인스턴스

end module

해당 포스팅은 신경욱 교수님의 강의를 기반으로 만들어졌습니다.

728x90

'임베디드 AI > FPGA' 카테고리의 다른 글

| Top module 이란 (0) | 2025.04.29 |

|---|---|

| FPGA(4) Verilog HDL 연산자 (1) | 2025.04.01 |

| FPGA(3) _ Verilog HDL 개요 (3) (0) | 2025.03.31 |

| FPGA 공부 (1)_Velilog 개요 (0) | 2025.03.31 |

| FPGA 공부 (0) | 2025.03.31 |

댓글