테스트 벤치 모듈

: HDL 모델을 시뮬레이션 하기 위한 Verilog 모듈

- DUT에 인가될 시뮬레이션 입력을 생성하는 구문

- 시뮬레이션 대상이 되는 모듈(Design Under Test; DUT)의 인스턴스

- 시뮬레이션 입력에 대한 DUT의 반응(response)을 관찰하는 구문

테스트 벤치 모듈 예제

module test_fix ();

reg A, B, C;

circuit c1(A, B, C, Out); //시뮬레이션 할 모듈 입력

initial begin // initial -> 합성 X, 오직 sim에서만 진행, begin~end 1회만 진행, 절차형 할당문

A=0; B=1; C=0;

#50 A=1; // '#' -> 1. 지연 (할당문) 2. parameter 값 변경

#50 A=0; C=1;

#50 C=0;

#50 $finish; // '$' -> 시스템 task를 의미

end

endmodule

Verilog 어휘 규칙

1. 어휘 토큰 (lexicl tokens)

-- 여백(white space)

빈칸(space), 탭(tab), 줄바꿈

어휘 토큰들을 분리하기 위해 사용되는 경우를 제외하고는 무시

공백과 탭은 문자열에서 의미있게 취급

-- 주석(comment)

HDL 소스코드의설명을위해사용되며, 컴파일과정에서무시됨

단일라인주석문; // 로시작되어해당라인의끝까지

블록주석문; /* ~ */ 로표시

(블록주석문은내포(nested)될수없음)

-- 연산자(operator)

단항연산자, 2항연산자, 3항연산자

-- 수(number)

- 정수형(integer) ; 10진수, 16진수, 8진수, 2진수

- 형식 : [size_constant] '<base_format> <number_value>

- [size_constant] -> 생략할 수 있는 옵션

: 비트 크기를 나타내는 상수 (생략 시 32bit로 내부적으로 표현됨)

- '<base_format>

: 밑수(base)를 결정 (10진수: d,D 16진수: h,H 8진수: o,O 2진수: b,B)

- <number_value>

: 밑수에 맞춰 기입 (x: 0이든 1이든 상관 ㄴㄴ, z: high impedence)

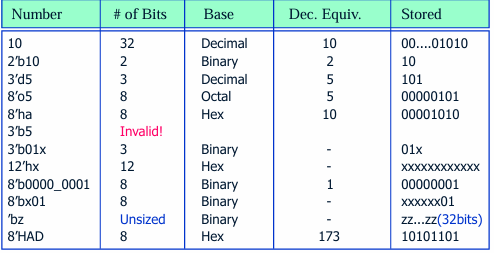

- 예시

- 비트 크기과 밑수를 가지지 않는 단순 10진수는 signed 정수로 표기

- 부호 지정자 없이 밑수만 지정되면 unsigned 정수로 취급

- 음수는 2의 보수 형식으로 표현됨

- 값에 ?가 사용되면 z로 취급

// MSB 자동 삽입

reg [11:0] a, b, c, d; //[11:0] -> 12bit

initial begin

a = 'hx; // yields xxx

b = 'h3x; // yields 03x

c = 'hz3; // yields zz3

d = 'h0z3; // yields 0z3

endex) 실수형 표현: 1.2E12 = 1.2 X 10^12

-- 문자열(string)

- " " 사이에 있는 일련의 문자들

- 여러 라인에 걸친 문자열 사용 X (단일 라인)

- 8비트 ASCII 값 -> unsigned 정수형 상수로 취급

- 문자열 변수는 reg형 변수이며, 문자 수에 8을 곱한 비트 폭을 가짐

-- 식별자(identifier)

- 고유의 이름을 지정하기 위해 사용

- 대소문자를 구별하여 인식

- 식별자: 알파벳, 숫자, 기호 $, 밑줄로 작성

- 첫번째는 숫자나 $ 사용 안됨

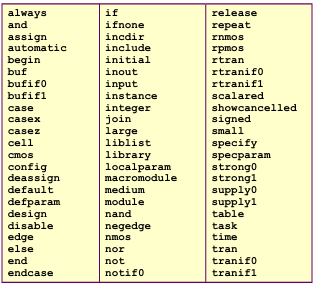

-- 키워드(keyword)

시스템 task 지시어 -> '$'

컴파일러 지시어 -> '`'(accent grave)

해당 포스팅은 신경욱 교수님의 강의를 기반으로 만들어졌습니다.

'임베디드 AI > FPGA' 카테고리의 다른 글

| Top module 이란 (0) | 2025.04.29 |

|---|---|

| FPGA(4) Verilog HDL 연산자 (1) | 2025.04.01 |

| FPGA(2)_Verilog HDL 개요(2) (0) | 2025.03.31 |

| FPGA 공부 (1)_Velilog 개요 (0) | 2025.03.31 |

| FPGA 공부 (0) | 2025.03.31 |

댓글